MIPS CPU

Project information

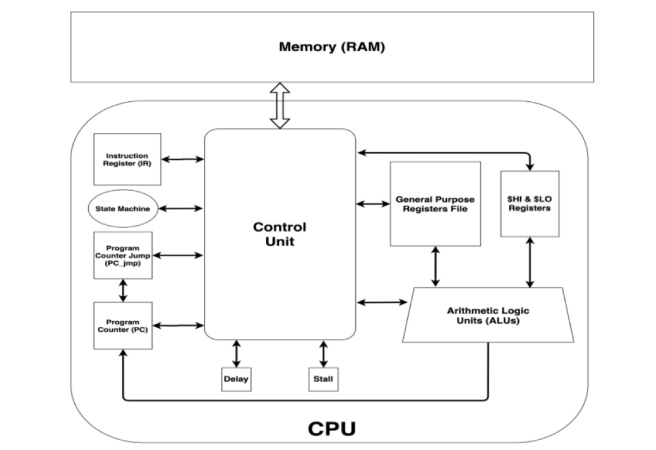

Created a fully functional, synthesizable processor in verilog in a team of 5, compliant with the MIPS instruction set specification (Revision 3.2) and capable of interacting with any Avalon compatible memory interface. Also includes an independent test-bench with randomised memory stalls which can be used to assert the functional correctness of any given CPU.

I worked on all aspects of implementation, and was responsible for the majority of the features, including CPU design, testbenching and workflow automation.